上拉电阻

在数字电路中,上拉电阻(英語:)是当某输入端口未连接设备或处于高阻抗的情况下,一种用于保证输入信号为预期逻辑电平的电阻元件。他们通常在不同的逻辑器件之间工作,提供一定的电压信号。[1][2]

原理

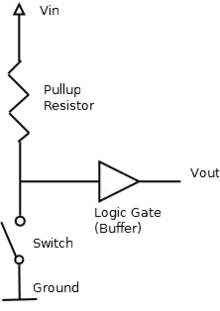

在上拉电阻所连接的导线上,如果外部组件未启用,上拉电阻則“微弱地”將输入电压信号“拉高”。当外部组件未连接时,对输入端来说,外部“看上去”就是高阻抗的。这时,通过上拉电阻可以将输入端口处的电压拉高到高电平。如果外部组件启用,它将取消上拉电阻所设置的高电平。通过这样,上拉电阻可以使引脚即使在未连接外部组件的时候也能保持确定的逻辑电平。[3]

下拉电阻

同样的,一个下拉电阻()以类似的方式工作,不过是与地()连接。它可以使逻辑信号保持在接近0伏特的状态,即使没有活动的设备连接在其所在的引脚上。

应用

一个上拉电阻可以设置在连接逻辑门和其输入端之间。例如,一个输入信号可以被一个电阻拉高,而一个开关或者带跳线可以将输入端和地相连。这可以被用作信息配置、选择,或者对外部设备信号进行检错纠错。

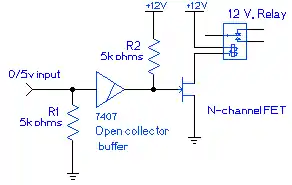

上拉电阻可以在逻辑设备不提供电流的时候工作。集电极开路就具有上拉电阻[3],这样的电路输出信号常常在驱动外部设备、组合逻辑电路、多个设备连接到一个总线的情况里应用。例如,右图所示的电路使用5伏特来激励一个中继器。如果左边的输入未连入,下拉电阻R1保证输入信号被拉低至低电平。7407TTL系列是一个集电极缓冲器,仅仅输出它所得到的输入信号。但是对于右边的器件来说,由于是TTL型器件,当它输出高电平的时候,它本身对右边的器件来说等效为未连接。这时,上拉电阻R2将输出信号上拉到12伏特,为下一级场效应管提供足够的电压使之导通,从而激活继电器。

上拉电阻可以和其他逻辑设备一起焊接在同一个电路板上。许多微控制器希望嵌入式控制应用程序使用内部的、可编程的上拉电阻,减少对外部组件的需求。[2]

缺点

上拉电阻的缺点是当电流流经时其将消耗额外的能量,并且可能会引起输出电平的延迟。某些逻辑芯片对于经过上拉电阻引入的电源供应瞬间状态较为敏感,这样就迫使为上拉电阻配置独立的、带有滤波的电压源。[2]

参考文献

- . Seattle Robotics Society. [2011年5月2日]. (原始内容存档于2011年6月13日).

- Paul Horowitz and Winfield Hill. . Cambridge, England: Cambridge University Press. 1989. ISBN 0-521-37095-7.

- 邓元庆、关宇、贾鹏、石会. . 北京: 清华大学出版社. ISBN 978-7-302-21406-9 (中文(中国大陆)).