DDR4 SDRAM

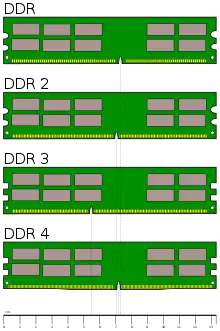

第四代雙倍資料率同步動態隨機存取記憶體(英文:Double-Data-Rate Fourth Generation Synchronous Dynamic Random Access Memory,簡稱為DDR4 SDRAM),是一種高頻寬的電腦記憶體規格。它屬於SDRAM家族的記憶體產品,是自1970年DRAM開始使用以來,現時最新的記憶體規格,旨在全面取代舊有的記憶體規格。[1]

.jpg.webp) | |

| 研發商 | JEDEC |

|---|---|

| 类型 | SDRAM |

| 发布日期 | 2014年 |

| 前代機種 | DDR3 SDRAM |

| 後繼機種 | DDR5 SDRAM |

| 類型 |

|---|

| RAM |

| 发展中 |

|

| 历史上 |

| ROM |

| NVRAM |

| 早期 |

| 磁式 |

| 光學式 |

| 发展中 |

| 历史上 |

DDR4-SDRAM提供比DDR3/DDR2-SDRAM更低的供電電壓以及更高的頻寬,但由於電壓標準、物理接口等諸多設計與DDR3-SDRAM等的不一致,因此DDR4-SDRAM與前代DDR3/DDR2/DDR等一樣,不會向下相容。現時,超微和英特爾兩大x86處理器廠商推出的大部分處理器產品都支援DDR4-SDRAM。

發展历史

JEDEC,記憶體標準的主體制定組織,在2005年時已經著手DDR3 SDRAM的繼任標準,[2]此時離DDR3標準亮相的2007年還有2年。[3][4]DDR4的高層級架構原定計劃在2008年完成。[5]

2007年開始就有DDR4標準的一些早前資訊被公開,[6]2008年8月份於三藩市舉行的英特爾開發者論壇(IDF)上,一位來自奇夢達的出席演講嘉賓提供更多關於DDR4的公開資訊。[6][7][8][9]當年關於DDR4的描述中,DDR4將使用30奈米製程、1.2伏的運行電壓、常規匯流排時脈速率在2133MT/s而“發燒級”的有3200MT/s、在2012年推出市場、在2013年它的運行電壓將改進至只有1伏。[7][9]

後來,在2010年於東京舉行的MenCon(一個電腦記憶體工業的大會)上,由JEDEC主導的題為“Time to rethink DDR4”的技術展示中,更多的DDR4技術資料被公佈。[10]當時以“New roadmap: More realistic roadmap is 2015”為題公佈DDR4記憶體標準的新時間線,使不少媒體站點報導DDR4的發布將會[11]或已定好[12][13]推遲至2015年。然而早在2011年初,三星電子、海力士已製造出並公佈全球首支DDR4-SDRAM記憶體模組工程樣品,這個時間剛好是原定計劃上,而且記憶體廠商也開始準備進行DDR4 SDRAM顆粒、模組的大規模商業化生產以達到計劃2012年推出市場的目標。[14]

預期計劃DDR4在2013年的DRAM市場上獲得5%的市場佔有率,[14]大約2015年普及並佔有50%的市佔率。[14]然而到2013年,DDR4的市場普及計劃被延期至2016年或以後。[15]DDR3至DDR4的市場普及過渡速度將比DDR2過渡至DDR3的要快上不少,DDR3花大約5年才從市場佔有率上超過DDR2。[16]在這個層面上,是由於現時升級DDR4 SDRAM需要連帶電腦系統的一些部件(如主機板、CPU)一併更換而致的。[17]

2009年2月,三星電子放出消息確認40奈米製程的DRAM晶片已成功流片,成為DDR4發展的關鍵一步。[18]自2009年開始,DRAM的製程僅開始遷移至50奈米。[19]2011年1月,三星電子宣布他們已經完成2GB的DDR4 DRAM模組的製造和測試,並公佈全球首支DDR4 SDRAM模組,其DDR4 DRAM顆粒基於30至39奈米之間的製程,[20]資料傳輸率為2133MT/s,運作電壓在1.2V,使用漏極開路(Open Drain)技術(從製造GDDR圖形記憶體的工藝改造而來[21])並且表現出比同規格DDR3模組低40%的耗電量。[20][22][23]

三個月以後(即2011年4月),海力士宣布運作於2400MT/s資料速率的2GB DDR4記憶體模組面世,運作電壓同樣在1.2V,也採用30至39奈米的製程(未具體指明),[14]另外他們還預期在2012年下半年開始大批量生產。[14]DDR4的半導體製程預期計劃是需要30奈米或更小長度的製程,預期將在2012年至2014年之間完成這個轉變。[16][24]

2012年5月,美光科技宣布他們將在2012年後期使用30奈米製程生產DRAM及快閃記憶體顆粒。[25]

在2012年7月,三星電子宣布試制業界首支16GB的寄存式雙列直插記憶體模組(registered dual inline memory modules,RDIMM),採用DDR4 SDRAM顆粒,用於企業級伺服器系統。[26][27]

2012年9月,JEDEC宣布DDR4 SDRAM的最終規格,正式成為DDR3 SDRAM的後繼記憶體標準。[28]起始資料傳送率由2133MT/s起跳,上限暫定為4266MT/s。

2014年4月,海力士宣布他們已經開發出世界上首支並且存儲密度最高的128GB的DDR4 SDRAM記憶體模組,基於使用20奈米製程級別的8Gb DDR4顆粒。該模組工作於2133MT/s,位寬64位元,資料頻寬為17GB/s。海力士預計2015年開始DDR4 SDRAM投入商業化,2016年將成為主流標準。[29]

未來市場發展

2013年4月,一名新聞作家對國際數據集團(IDG)旗下的國際數據資訊(IDC)的關於DDR4 SDRAM製造生產的相關調查發表看法。[30]其中指出,隨著行動式運算平台以及相關裝置的日益普及——它們都使用效能較低但極低功耗的記憶體,傳統桌上型運算平台的市場增長緩慢,以及記憶體廠商市場份額的鞏固以及製造流程業務的整合(即記憶體顆粒以及記憶體模組的製造同屬於記憶體廠商的業務,如三星電子),這些就意味著RAM行業的利潤空間將十分低下。結果就是他們會尋求保費定價的方式來保證營業利潤,以支持龐大的研發費用以向市場推出新技術,但是要做到這樣是十分困難的,而且市場容量已轉移至其它領域上;根據iSupply的報導指出,SDRAM製造商和晶片組開發者在某種程度上處於「進退兩難的境地」,「沒有人(消費者)願意花大錢購買DDR4的產品,而價位低,利潤也低,造成製造商對這產品的生意興致缺缺」。[30]市場情緒的轉變在於桌上型運算平台,而由英特爾、超微製造的支援DDR4的晶片組、處理器產品,可能會引領新一輪的記憶體市場增長。[30]

不過由於當前DDR4相較於DDR3的實際效能表現並不是十分出彩(除非運作時脈能有大幅度的提升),2015年下半年到2016年中時雖然DDR4記憶體每MB容量的價格比DDR3的低,然而這個時間段市面上支援DDR4的處理器較少,而這些處理器的效能對比DDR3世代的產品的也沒有明顯提升,主要依靠舊電腦的汰換升級來獲得市場普及機會;而到2017年時,儘管有更多的支援DDR4記憶體的處理器和主機板推出,由於各大記憶體晶片廠商的減產加上製程更新而導致的新一輪抬價,本來已經不佳的個人電腦出貨量則是持續灰暗光景,為DDR4全面取代DDR3的進程增添未知數。[31][32][33]

支援產品

實際可支援DDR4記憶體的主機板、處理器產品於2014年面世,包括英特爾、超微於2014年下半年發布的處理器。[14][25][34][35][36][37]2014年第二季度已經有帶有ECC校驗功能的產品推出市場,[38]無ECC校驗功能的型號在2014年第三季度推出。[39]超微在2014年發布的「Hierofalcon」系統晶片(SoC)開始支援DDR4記憶體。[40]而英特爾早在2014年Haswell-E的路線圖上計劃支援DDR4,2014年底發布的「Haswell-E」核心之處理器是英特爾首款支援DDR4 SDRAM的產品。[41]此時,已經有不少DDR4記憶體模組持續鋪貨中。[42]目前Intel的Coffe Lake、Kaby Lake、Skylake、Haswell-E和Broadwell-E處理器架構全面支持DDR4記憶體,而它們當中Kaby Lake和Skylake保留DDR3和LPDDR3的支援(LPDDR3主要是低功耗處理器,即型號中帶Y的產品線,它們禁用DDR4記憶體控制器)。

2014年8月下旬,英特尔发布支持DDR4内存,基于Haswell-E/EP核心的Core i7-5900/5800处理器系列以及配套的X99芯片组,支持四通道内存技术。是全球首款支援DDR4内存的处理器。此外還採用與LGA 2011不相容的LGA 2011v3插座,與使用DDR3記憶體的前代型號有所區分。[43]

2015年8月上旬,英特爾發布Skylake微架構的CPU,Core i7-6700K和Core i5-6600K以及Z170晶片組,支援DDR4。其後除了Core m系列不支援DDR4之外,Core i全系列型號均全數支援,不過這些處理器同時也支援DDR3L記憶體(低電壓版DDR3記憶體),只是DDR3L和DDR4不能同時使用,只能二者擇其一。

2016年8月,超微發表最後一代基於Bulldozer微架構、核心代號「Bristol Ridge」的AMD APU,僅支援DDR4 SDRAM,採用Socket AM4插座。[44]2017年3月發表的基於Zen微架構的Ryzen系列處理器上,這些處理器也使用Socket AM4,僅支援DDR4記憶體。

效能提升

與DDR3 SDRAM相比,DDR4 SDRAM擁有更高的時脈速率以及資料傳輸速率,初期支援2133至4266MT/s的資料傳輸率,而現行的DDR3,JEDEC制定的標準也僅從800至1600MT/s,後期才擴展至2133MT/s,非標準的也只有規格強大但產量較少的2400MT/s。[17][16][45]而且,在效能提升的前提下,還比DDR3 SDRAM擁有更好的功耗表現,得益於更高的記憶體顆粒製程以及DDR4有1.05V至1.2V的供電電壓(DDR3的為1.2V至1.65V),最大電流值僅和DDR3相當。[46]對於伺服器市場,還提供Banks切換特性,[16]但也就這樣使得伺服器用DDR4記憶體與桌面版本的DDR4記憶體從物理層面上就無法互用。

技術細節

DDR4相較於前代的DDR3的優勢,主要是更高的模組密度(容量單位體積容量更大)、操作電壓更低(功耗降低)以及頻寬增加三方面。

容量

相較於DDR3,DDR4理論上每根DIMM模組能達到512GiB的容量,而DDR3每個DIMM模組的理論最大容量僅128GiB[47];一個rank單元內的bank單元數量增長至16個(4個bank選擇位元),每個DIMM模組最高擁有8個rank單元。[48]:16

DDR4為提升資料存儲密度,達到預定的容量目標,可能選擇矽穿孔製程或其它3D堆疊製程。.[17][16][49][50]DDR4的規格中一開始也包含有標準的3D堆疊製程,[50]最大的堆疊層數可達一顆DRAM顆粒8層晶片堆疊封裝。[48]:12X-bit Labs預料如果採用這樣高成本的高規格製程,將會導致高密度DDR4顆粒的價格非常的昂貴。[17]記憶體預取依舊是8n[48]:16帶bank群組,包括兩個或4個可選擇的bank群組。[51]另外在伺服器平台上,還可選可切換記憶體bank的功能。[16][49]

2008年一本關於半導體製程的書籍《Wafer Level 3-D ICs Process Technology》受到了關注,無標明製程的類比電子元件,例如電荷泵浦(charge pump)以及穩壓器,另外額外的電路「可允許增加一定的特定頻寬,但這樣會消耗更多的晶圓面積」。這樣的例子有CRC錯誤校驗、片上終端、突發式硬體(burst hardware)、可程式管線、低阻抗,以及對感測放大器的需求越來越多(由於低工作電壓而導致的位線的電平會有下降的可能)。該書的作者也指出,這樣的結果導致記憶體陣列本身用到的晶圓面積佔記憶體晶片的面積比,隨著時間推移,下降至SDRAM、DDR晶片的70%至78%,DDR2的47%,DDR3的38%,DDR4更可能低至30%以下。[52]

DDR4規格中也為x4、x8、x16等記憶體裝置定義了標準。[53]

資料傳輸

最初三星的技術文檔中表示DDR4的資料傳輸率也從2133MT/s起跳,[48]:18最高速率在2013年的標準中暫定為4266MT/s[17],由於當時已有一些超頻版DDR3記憶體模組已能上探至2133MT/s的資料傳輸率,因此為了與DDR3拉開效能差距而將最低資料傳輸率定為2133MT/s。[17][16]Techage報導三星電子於2011年製造的DDR4 SDRAM記憶體模組的工程樣品中,CAS延時值為13個時鐘週期,與DDR3的相比,延時值增長幅度和DDR2升級至DDR3時差不多。[21]至2012年,JEDEC正式確定DDR4 SDRAM的標準後,其資料傳輸率僅從1600MT/s起跳,但是以來其記憶體陣列的核心時脈比DDR3的翻倍,達200MHz~400MHz,而I/O匯流排時脈也從DDR3 SDRAM的400MHz~1066MHz提升至DDR4 SDRAM的800至1600MHz,不過I/O Buffer預取仍和DDR3一樣維持8n倍率。[54][lower-alpha 2]由於DDR4記憶體的預取沒有變動,僅以拉升運作時脈來提升傳輸率、傳輸延時也較高,而恰恰初面世時DDR4的運作時脈有普遍較低(1866~2400MT/s之間,更高的規格又多為XMP/AMP超頻設定檔來產生),這麼低的運作時脈下實際的效能表現相比DDR3的並不會有太多出彩之處,除非大幅度地提升時脈。不過在2017年,一些有實力的廠商已經能將DDR4記憶體模組的資料傳輸率設定至3200MT/s之譜並能穩定運行,頻寬表現也足夠突出。[56]

傳輸協議還有些以下改變:[48]:20

供電

新技術使用最高1.2V的記憶體模組供電電壓,[48]:16[57][58],最大字線電壓峰值2.5V(VPP)[48]:16,相對地,DDR3的模組供電電壓為1.5V;2013年釋出的技術說明中,DDR4最低供電電壓為1.05V(DDR4L),而至相對的是DDR3的低電壓版本DDR3L以及DDR3U,最低也分別僅1.35V和1.25V(截至2014年8月)。[59]

命令編碼

儘管運行方式與前代的DDR3、DDR2等基本相同,而DDR4還是相對於前幾代SDRAM的命令格式上作出了修改。一個新命令信號「/ACT」用來指示激活(open row,開行)命令。

激活命令需要比任何其它的命令更多的位址位元數(在一個8Gb的部分需要18列位址位元數),因此當 /ACT 命令處於高電平時其高位元是閒置時,標準的「/RAS」、「/CAS」以及「/WE」信號是和位址位元的高位共用的。先前已編碼的一個激活命令是不使用 /RAS=L、/CAS=H 以及 /WE=H 這樣的組合的。

就如以往的SDRAM編碼,A10被用於選取命令變體:自動預充電存取命令,和對單個bank單元與全部bank單元預充電命令的選取。它也選取ZQ校準命令的兩個變體。

另外,A12被用作請求突發突變(burst chop):在 4 transfers 進行以後截斷一個 8-transfer 突發。儘管直到8個傳輸時間過去之前bank仍然處於忙碌狀態並且其他命令不可用,不同的bank可供存取。

同樣,bank的位址數量也被大幅提升。每個DRAM裏有4個bank選取位元可用來選取多達16個bank單元:兩個bank位址位元(BA0、BA1),和兩個bank群組位元(BG0、BG1)。當在同一個bank群組中存取不同的bank單元時會有另外的時間限制;在不同的bank群組中,存取一個bank比以往的更快。

另外,3個晶片層選取信號(C0、C1、C2),允許最多8個堆疊式晶片層封裝於一塊DRAM封裝上。這可以更有效地充當3個以上的bank單元選取位元,使選取總數達到7(可以定位128個bank單元)。

| /CS | BGn, BAn | /ACT | A17 | A16 /RAS | A15 /CAS | A14 /WE | A13 | A12 | A11 | A10 | A9–0 | 命令 |

|---|---|---|---|---|---|---|---|---|---|---|---|---|

| H | X | 無選取(無操作) | ||||||||||

| L | bank | L | 行位址 | 啟動(激活):開啟一行 | ||||||||

| L | V | H | V | H | H | H | V | 無操作 | ||||

| L | V | H | V | H | H | L | V | long | V | ZQ校準 | ||

| L | bank | H | V | H | L | H | V | BC | V | AP | 列 | 讀取(BC=burst chop,突發突變) |

| L | bank | H | V | H | L | L | V | BC | V | AP | 列 | 寫入(AP=auto-precharge,自動預充電) |

| L | V | H | V | L | H | H | V | (未分配,保留) | ||||

| L | V | H | V | L | H | L | V | H | V | 對所有bank單元進行預充電 | ||

| L | bank | H | V | L | H | L | V | L | V | 對某個bank單元進行預充電 | ||

| L | V | H | V | L | L | H | V | 刷新 | ||||

| L | register | H | 0 | L | L | L | 0 | 資料 | 模式暫存集合(Mode register set,MR0–MR6) | |||

注:

- 信號電平

- H,高電平

- L,低電平

- V,高電平或低電平的有效信號(代表「0」和「1」的有效電平)

- X,無關

- 邏輯圖例

- 有效

- 無效

- 不相關

舊有的標準傳輸率僅為1600、1866、2133以及2400MT/s[60](12/15,14/15,16/15以及18/15GHz的時脈速率,雙倍資料率),2666和3200MT/s(20/15以及24/15GHz的時脈速率)也有提供,但當時的規格尚未落定。

設計考量

美光科技的DDR4研發團隊釋出了一些積體電路(IC)以及印刷電路板(PCB)的關鍵設計要點:[61]

積體電路設計:[61]

- VrefDQ測定校準(DDR4「要求VrefDQ測定校準要由控制器來執行」);

- 新式尋址排程解決方案(「bank組群」,ACT_n取代RAS#、CAS#以及WE#命令,PAR以及Alert_n用於錯誤檢查,DBI_n用於資料匯流排倒轉/翻轉);

- 新式節電特性(低能耗自動自刷新,溫度控制刷新,細粒度刷新,資料匯流排倒轉/翻轉,CMD/ADDT延時/潛伏);

- 新式供電(VDD/VDDQ為1.2V電壓,字線升壓峰值(即VPP)為2.5V);

- VrefDQ必須供給至DRAM內,而VrefCA由外部(如主機板、顯卡等)供給;

- DQ腳位高電平終止使用偽開放汲極 I/O(不同於DDR3由中心腳位至VTT的CA腳位)

模組封裝

DDR4有數種封裝規格。

一種是288 PIN U-DIMM模組,與240 PIN的DDR2/DDR3 DIMM模組相近,供普通的桌上型電腦使用。[62][48]:11每個PIN的之間的寬度極其接近(而每個PIN的寬度改為0.85毫米而非1.0毫米)以便符合標準的5¼英寸(133.35-)的DIMM模組寬度,標準的模組高度小幅增加到(31.25 mm/1.23英寸而非30.35 mm/1.2英寸)以使信號佈線更容易,模組厚度也從1.0毫米增加到1.2毫米以容納更多的信號層。

另有288 PIN的R-DIMM模組,供伺服器主機板使用,除PIN數量、更精確更精確的電氣效能要求(但和U-DIMM一樣是1.2V工作電壓)、支援ECC以外,和U-DIMM相近,但和U-DIMM不能互用。[62]

260 PIN的SO-DIMM(DDR3 SO-DIMM擁有204 PIN),每個PIN的寬度是0.5毫米(DDR3 SO-DIMM的為0.6毫米),模組整體長度由DDR3的67.6毫米增加到68.6毫米,但高度保持30毫米不變。[48]:11

模組型號

JEDEC標準DDR4模組

| 標準名稱 | 記憶體時脈 (MHz) |

I/O匯流排時脈 (MHz) |

資料傳輸率 (MT/s) |

模組名稱 | 峰值頻寬 (MB/s) |

時序 (CL-tRCD-tRP) |

CAS延時週期 (ns) |

|---|---|---|---|---|---|---|---|

| DDR4-1600J* DDR4-1600K DDR4-1600L | 200 | 800 | 1600 | PC4-1600 或 PC4-12800 | 12800 | 10-10-10 11-11-11 12-12-12 | 12.5 13.75 15 |

| DDR4-1866L* DDR4-1866M DDR4-1866N | 233.33 | 933.33 | 1866.67 | PC4-1866 或 PC4-14900 | 14933.33 | 12-12-12 13-13-13 14-14-14 | 12.857 13.929 15 |

| DDR4-2133N* DDR4-2133P DDR4-2133R | 266.67 | 1066.67 | 2133.33 | PC4-2133 或 PC4-17000 | 17066.67 | 14-14-14 15-15-15 16-16-16 | 13.125 14.063 15 |

| DDR4-2400P* DDR4-2400R DDR4-2400U | 300 | 1200 | 2400 | PC4-2400 或 PC4-19200 | 19200 | 15-15-15 16-16-16 18-18-18 | 12.5 13.33 15 |

| DDR4-2666T DDR4-2666U DDR4-2666V DDR4-2666W | 325 | 1333 | 2666 | PC4-21333 | 21333 | 17-17-17 18-18-18 19-19-19 20-20-20 | 12.75 13.50 14.25 15 |

| DDR4-2933V DDR4-2933W DDR4-2933Y DDR4-2933AA | 366.6 | 1466.5 | 2933 | PC4-23466 | 23466 | 19-19-19 20-20-20 21-21-21 22-22-22 | 12.96 13.64 14.32 15 |

| DDR4-3200W DDR4-3200AA DDR4-3200AC | 400 | 1600 | 3200 | PC4-25600 | 25600 | 20-20-20 22-22-22 24-24-24 | 12.50 13.75 15 |

* 可選項

- CL(CAS Latency)- 從發送一個行位址信號到記憶體與記憶體響應並開始資料傳輸之間的時鐘信號週期

- tRCD - 列啟用與讀寫操作之間的時鐘週期

- tRP - 列預充電操作和列啟用操作之間的時鐘週期

此回,DDR4-xxxx以及PC4-xxxx中的「xxxx」都代表資料傳輸率(MT/s),「DDR4-xxxx」適用於記憶體晶片而「PC4-xxxx」則用於已組裝完成的DIMM記憶體模組。此前DDR3以及更早的模組,標示記憶體的頻寬(MB/s),所以像是PC4-1866對比PC3-14900,它們的頻寬是一樣的。模組的峰值頻寬,由資料傳輸率/每秒的資料吞吐量乘以8。乘以8是由於DDR4記憶體模組的資料匯流排為64位元,以此除以8位元每字節而得。

不過往後的標準模組,型號又全數回到原來PCx-xxxxx,頻寬數值標示於型號上。

腳註

注釋

- 實際上這個包裝盒内是4支DDR4 RDIMM模組,由圖中可以見到其中的3支,兩支可以見到標簽和記憶體晶片。

- 但是DDR3 SDRAM的JEDEC標準可達2133MT/s於1066MHz的I/O匯流排時脈下,而且原生1600MT/s的DDR3 SDRAM晶片、模組也有大量生產,超頻至2133MT/s甚至2400MT/s的,或是低時序的DDR3 1600MT/s、1866MT/s的模組也不在少數。[55]

參考資料

- (PDF), www.ieee.org: 10, 2008 [2012-01-23], (原始内容存档 (PDF)于2011-06-04)

- Sobolev, Vyacheslav. . digitimes.com. 2005-05-31 [2011-04-28]. (原始内容存档于2013-12-03).

“DDR3以後的記憶體技術都已經著手研究中。JEDEC一直按照標準化進程劃分記憶體世代層級:現有世代、下一世代以及其未來,三個世代”原文:Initial investigations have already started on memory technology beyond DDR3. JEDEC always has about three generations of memory in various stages of the standardization process: current generation, next generation, and future.

- (PDF). Kingston Technology. [2011-04-28]. (原始内容 (PDF)存档于2011-07-28).

"DDR3 memory launched in June 2007"

- Valich, Theo. . The Inquirer. 2007-05-02 [2011-04-28]. (原始内容存档于2010-02-05).

- Hammerschmidt, Christoph. . eetimes.com. 2007-08-29 [2011-04-28]. (原始内容存档于2012-10-02).

- . The "H" (h-online.com). 2008-08-21 [2011-04-28]. (原始内容存档于2011-05-26).

約一年前JEDEC標準化委員會已指出指標。原文:The JEDEC standardisation committee cited similar figures around one year ago

- Graham-Smith, Darien. . PC Pro. 2008-08-19 [2011-04-28]. (原始内容存档于2011-06-07).

- Volker Risska (Volker Rißka). . computerbase.de. 2008-08-21 [2011-04-28]. (原始内容存档于2019-09-24). (English 页面存档备份,存于)

- Novakovic, Nebojsa. . The Inquirer. 2008-08-19 [2011-04-28]. (原始内容存档于2010-11-25).

- Gervasi, Bill. (PDF). July 2010. Discobolus Designs. [2011-04-29]. (原始内容 (PDF)存档于2011-08-14).

- ciw. . heise.de. 2010-08-17 [2011-04-29]. (原始内容存档于2011-04-09). (English 页面存档备份,存于)

- Nilsson, Lars-Göran. . semiaccurate.com. 2010-08-16 [2011-04-29]. (原始内容存档于2011-05-20).

- By 'annihilator'. . wccftech.com. 2010-08-18 [2011-04-29]. (原始内容存档于2010-08-23).

- Marc. . behardware.com. 2011-04-05 [2012-04-14]. (原始内容存档于2012-04-15).

- Shah, Agam. "Adoption of DDR4 memory faces delays" 页面存档备份,存于, TechHive (IDG), April 12, 2013. Retrieved on June 30, 2013.

- 後藤 弘茂 ("Gotou Shigehiro"). . 2010-08-16. PC Watch (Japan). [2011-04-25]. (原始内容存档于2011-09-06). (English translation)

- Shilov, Anton, , Xbitlabs.com, 2010-08-16 [2011-01-03], (原始内容存档于2010-12-19)

- Gruener, Wolfgang. . tgdaily.com. February 4, 2009 [2009-06-16]. (原始内容存档于2009-05-24).

- Jansen, Ng. . dailytech.com. January 20, 2009 [2009-06-17]. (原始内容存档于2009-06-22).

- . Samsung. 2011-04-11 [26 April 2011]. (原始内容存档于2012-10-15).

- Perry, Ryan. . techgage.com. 2011-01-06 [2011-04-29]. (原始内容存档于2011-02-10).

- . Samsung. 2011-01-04 [2011-03-13]. (原始内容存档于2011-04-16).

- Protalinski, Emil, , Techspot.com, 2011-01-04 [2012-01-23], (原始内容存档于2011-12-09)

- . 2010-08-146. PC Watch (Japan). [2011-04-25]. (注意PC Watch的文章日期是2010年8月16日)

- , engadget.com, 2012-05-08 [2012-05-08], (原始内容存档于2012-05-11)

- . [2014-07-29]. (原始内容存档于2013-11-04).

- . [2014-07-29]. (原始内容存档于2014-10-27).

- . [2014-07-29]. (原始内容存档于2014-04-12).

- Shah, Agam. . IDG News. 2013-04-12 [22 April 2013]. (原始内容存档于2013-05-09).

- . TechNews 科技新報. [2017-11-05]. (原始内容存档于2017-11-07) (中文(台灣)).

- . 中時電子報. [2017-11-05]. (原始内容存档于2017-11-07) (中文(台灣)).

- . www.cmmedia.com.tw. [2017-11-05]. (原始内容存档于2017-11-07).

- . [2013-08-31]. (原始内容存档于2013-08-31).

- . [2014-05-01]. (原始内容存档于2014-03-24).

- . [2014-05-01]. (原始内容存档于2014-07-29).

- . [2014-05-01]. (原始内容存档于2014-05-25).

- Rodger, Andrew; Lunny, Joan. . The Wall Street Journal (The Wall Street Journal). 2014-06-02 [2014-06-04]. (原始内容存档于2014-06-06).

Crucial, a leading global brand of memory and storage upgrades, is now shipping DDR4 server memory.

- Vättö, Kristian. . AnandTech (AnandTech). 2014-06-04 [2014-06-04]. (原始内容存档于2014-06-05).

Availability is slated for August but pricing has yet to be announced.

- . [2014-07-30]. (原始内容存档于2014-11-29).

- . [2014-07-30]. (原始内容存档于2014-10-15).

- . TechPowerUp. [28 April 2015]. (原始内容存档于2015-08-12).

- 王者中的王者,Core i7-5960X处理器、X99主板评测 页面存档备份,存于 - expreview.com

- Burke, Steve. . Gamer Nexus. 5 September 2016 [6 September 2016]. (原始内容存档于2016-09-10).

- . [2014-05-01]. (原始内容存档于2014-05-02).

- . [2014-05-01]. (原始内容存档于2014-01-28).

- . EE Times. [2016-01-09]. (原始内容存档于2016-03-04).

- Jung, J.Y., , , Samsung, 2012-09-11 [2012-09-15], (原始内容存档于2012-11-27)

- Swinburne, Richard. . bit-tech.net. 2010-08-26 [2011-04-28]. (原始内容存档于2011-03-10). – Page 1 页面存档备份,存于 – Page 2 页面存档备份,存于 – Page 3 页面存档备份,存于

- . JEDEC. 2011-03-17 [26 April 2011]. (原始内容存档于2014-08-20).

- . jedec.org. [2012-04-14]. (原始内容存档于2012-04-01).

- Tan, Gutmann and Reif. . Springer. 2008: 278 (sections 12.3.4–12.3.5) [2014-07-30]. (原始内容存档于2014-06-09).

- (PDF). JEDEC Standard No. 79-4. [SEPTEMBER 2012]. (原始内容 (PDF)存档于2013-12-03).

- . JEDEC. July 2012 [2015-07-18]. (原始内容存档于2015-06-27).

- . Corsair. [17 July 2015]. (原始内容存档于2016-03-05).

- . [2017-05-11]. (原始内容存档于2017-05-04).

- , Pcpro.co.uk, 2008-08-19 [2012-01-23], (原始内容存档于2019-09-24)

- , Heise-online.co.uk, 2008-08-21 [2012-01-23], (原始内容存档于2008-12-20)

- , , [2014-08-20], (原始内容存档于2016-03-24).

- , JEDEC Solid State Technology Association, September 2012 [2012-10-11], (原始内容存档于2012-09-28). Username "cypherpunks" and password "cypherpunks" will allow download.

- . Denali Memory Report, a memory market reporting site. 2012-07-26 [22 April 2013]. (原始内容存档于2013-12-02).

- tandee. . T客邦. [2014-07-30]. (原始内容存档于2014-08-08).

- (PDF), JEDEC

- (PDF), JEDEC

外部連結

JEDEC官方頁面

媒體報導

- 你真的了解DDR4么?看官方全景讲解页面存档备份,存于(简体中文)

- 盼星星盼月亮 DDR4标准规范终于公布!页面存档备份,存于(简体中文)

- 記憶體10年技術演進史,系統顆粒DDR與顯示顆粒GDDR差在哪?页面存档备份,存于(繁體中文)

- DDR4 記憶體即將導入個人電腦平台,簡單看懂改朝換代的意義页面存档备份,存于(繁體中文)

- 二進位的世界:記憶體發展簡史 _ DDR4 VS. DDR3 效能評測页面存档备份,存于(繁體中文)